Renesas Electronics RZ/T2L Hochleistungs-MPU mit EtherCAT

Die Renesas Electronics RZ/T2L Hochleistungs-MPU mit EtherCAT realisiert eine Hochgeschwindigkeits-Verarbeitung und eine hochpräzise Echtzeitsteuerung. Der RZ/T2L ermöglicht Benutzern die einfache Skalierung der Produktentwicklung durch das Angebot einer ähnlichen Hardware-Architektur (H/W) wie der RZ/T2M und einer skalierbaren/kompatiblen Software-Plattform (S/W) mit MPU und MCU von Renesas. Das in einem 196-Pin-FBGA-Gehäuse mit einem Rastermaß von 12 mm2 x 0,8 mm untergebrachte Bauteil wird in einem Temperaturbereich von -40 °C bis +125 °C betrieben.Merkmale

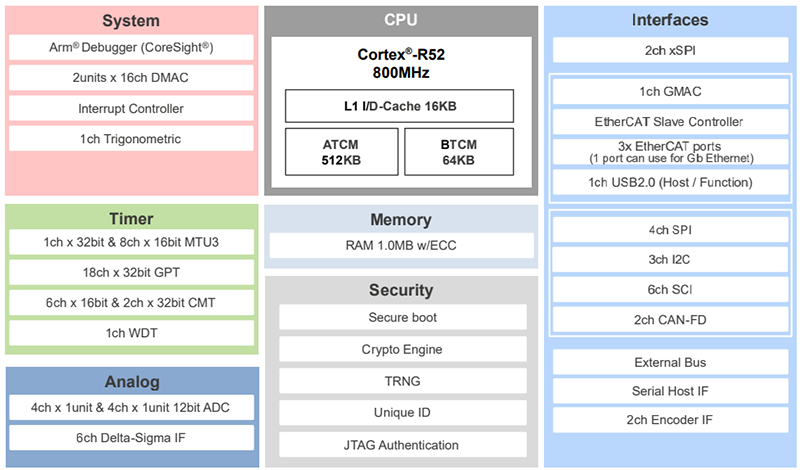

- Integrierter Arm® Cortex- R52 bei max. 800 MHz, ein eng gekoppelter Speicher (576 KB), der direkt mit der CPU und dem LLPP-Bus (Low Latency Peripheral Port) verbunden ist

- Integrierte umfangreiche Peripheriefunktionen, wie z. B. ΣΔ-I/F, A/D-Wandler und Multiprotokoll-Encoder-I/F

- Nahtlose H/W-Architektur mit RZ/T2M und skalierbaren/kompatiblen S/W-Plattformen, wie z. B. FSP mit Renesas MPU und MCU

- Integrierter EtherCAT-Slave-Controller und unterstützt ECC für alle internen RAM

- Unterstützt Sicherheitsfunktionen, wie z. B. sicheres Booten, JTAG-Authentifizierung und einzigartige ID

- Kann als Sicherheits-MCU in der funktionalen S/W-Lösung verwendet werden

- Leistungsstarke Echtzeitsteuerung

- Motorsteuerungssystem auf einem Einzelchip

Applikationen

- AC-Servos

- Umrichter

- Industrieroboter

- Medizinische Geräte

- Windturbinen

- Aufzüge

Technische Daten

- Einzelner 32-Bit Arm® Cortex-R52 Prozessor auf dem Chip

- Hochgeschwindigkeits-Echtzeitsteuerung mit einer Betriebsfrequenz von 200 MHz bis 400 MHz

- 512KB/64KB Tightly Coupled Memory (TCM) mit ECC

- Befehls-Cache/Daten-Cache mit ECC,{sp}16KB pro Cache

- Hochgeschwindigkeitsunterbrechung

- Die FPU unterstützt Additions-, Subtraktions-, Multiplikations-, Divisions-, Multiplikations- und Akkumulations- sowie Quadratwurzeloperationen in einfacher und doppelter Genauigkeit.

- NEON und Advanced SIMD unterstützen Integer- oder Single-Precision-Ergebnisse

- Harvard-Architektur mit 8-stufiger Pipeline

- Unterstützt die Speicherschutzeinheit (MPU)

- Die Arm CoreSight-Architektur unterstützt das Debugging über JTAG- und SWD-Schnittstellen

- Niedriger Stromverbrauch mit Standby-Modus und Modul-Stopp-Funktion

- On-Chip-SRAM

- 1.0MB des On-Chip SRAM mit ECC

- 150/200MHz

- Datenübertragung (DMAC: 16 Kanäle × 2 Einheiten)

- Ereignis-Link-Controller

- Moduloperationen können durch EreignisSignale und nicht durch Interrupts gestartet werden

- Der verknüpfte Betrieb von Modulen ist auch dann möglich, wenn sich die CPU im Standby-Zustand befindet

- Reset und Steuerung der Versorgungsspannung, vier Reset-Quellen (einschließlich eines Pin-Resets)

- Taktfunktionen

- 25MHz externe Takt-/Oszillator-Eingangsfrequenz

- 200/400/800MHz oder 150/300/600MHz CPU-Taktfrequenz

- 200MHz oder 150MHz Systemtaktfrequenz

- 240kHz Langsamer On-Chip-Oszillator (LOCO)

- Sicherheitsfunktionen

- Register-Schreibschutz, Erkennung des Stopps der Eingangstaktschwingung und CRC

- Master-Speicherschutzeinheit (MPU)

- Sicherheitsfunktionen (optional)

- Bootmodus mit Sicherheit durch Verschlüsselung

- JTAG-Authentifizierung

- Kryptologischer Beschleuniger

- TRNG

- Encoder-Schnittstellen

- Bis zu 2x Kanäle

- EnDat 2.2, BiSS-C, A-Format und HIPERFACE DSL-konforme Schnittstellen

- Frequenzgeteilter Ausgang von einem Encoder

- Kommunikationsschnittstellen

- Ethernet

- 3x Port EtherCAT-Slave-Steuerung

- Ethernet-MAC mit Einzelanschluss

- Einkanal-USB 2.0 Hochgeschwindigkeits-Host-/Funktionen

- Zwei Kanal-CAN/CANFD (konform mit ISO11898-1)

- 6-Kanal-SCI mit 16-Byte-Übertragungs - und Empfangs-FIFOs

- Dreikanal-I2C-Bus-Schnittstelle für die Übertragung von bis zu 400 KBit/s

- Vier Kanal-SPI

- 2-Kanal-xSPI

- Ethernet

- Externe serielle Host-Schnittstelle (SHOSTIF)

- Externer Adressbereich

- Busse für Hochgeschwindigkeitsdatenübertragung mit bis zu 100 MHz

- Unterstützung für bis zu 4 CS-Bereiche

- 8- oder 16-Bit-Busfläche pro Bereich wählbar

- Bis zu 35 x Timer mit erweiterter Funktion

- 16-Bit x 8 + 32-Bit MTU3 (9 Kanäle), 32-Bit GPT (18 Kanäle): Eingangserfassung, Ausgangsvergleich, PWM-Wellenform-Ausgang

- 16-Bit CMT (6 Kanäle), 32-Bit CMTW (2 Kanäle)

- ΔΣ-Schnittstelle, bis zu 6 x ΔΣ-Modulatoren, die extern verbunden werden können

- Einheit mit trigonometrischen Funktionen

- Gleichzeitige Berechnung von Sinus und Kosinus

- Gleichzeitige Berechnung von Arkustangens und hypot_k

- 12-Bit A/D-Wandler, 12 Bit × 2 Einheiten (4 Kanäle für Einheit 0 und 1)

- Temperatursensor zur Messung der Temperatur innerhalb des Chips

- Universal-I/O-Anschlüsse

- Eingangs-Pull-up/-Pull-down

- Die Positionen der Eingangs-/Ausgangsfunktionen für Peripheriemodule können unter mehreren Pins ausgewählt werden

- Betriebstemperaturbereich: -40 °C bis +125 °C

- 196-Pin-FBGA-Gehäuse von 12 mm2 x 0,8 mm

Blockdiagramm

Evaluierungskit anzeigen

Veröffentlichungsdatum: 2023-03-20

| Aktualisiert: 2026-01-02