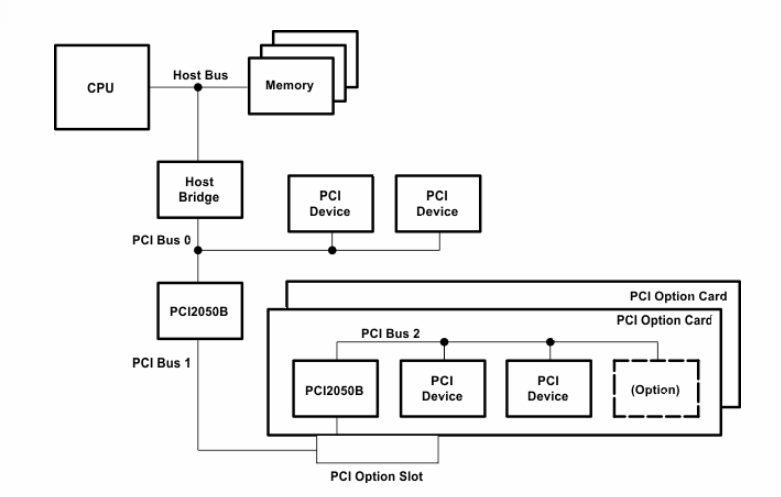

Texas Instruments PCI2050B PCI-zu-PCI-Brücke

Die Texas Instruments PCI2050B PCI-zu-PCI-Brücke verfügt über einen leistungsstarken Verbindungspfad zwischen zwei PCI-Bussen (Peripheral Component Interconnect, PCI), der mit einer maximalen Busfrequenz von 66 MHz betrieben wird. Transaktionen erfolgen zwischen den Mastern auf einem und den Zielen auf einem anderen PCI-Bus. Die PCI2050B Brücke ermöglicht die gleichzeitige Durchführung von überbrückten Transaktionen auf beiden Bussen. Die PCI-zu-PCI-Brücke unterstützt Burst-Modus-Übertragungen zur Maximierung des Datendurchsatzes und die beiden Bus-Datenverkehrspfade durch die Brücke arbeiten unabhängig voneinander.Die PCI2050B Brücke von TI ist mit der PCI-Local-Bus-Spezifikation konform und wird verwendet, um die elektrischen Ladegrenzen von 10 Bauteilen pro PCI-Bus und ein PCI-Bauteil pro Erweiterungssteckplatz durch die Erstellung von hierarchischen Bussen zu überwinden. Die PCI2050B bietet eine zweistufige interne Arbitrierung für bis zu neun sekundäre Bus-Master und kann mit einem externen Bus-Arbiter implementiert werden.

Die erweiterte CompactPCI™ Hot-Swap-PCI-Funktion macht die PCI2050B Brücke zu einer idealen Lösung für kompakte Multifunktions-PCI-Karten und zur Anpassung von Einzelfunktionskarten an die Hot-Swap-Konformität.

Merkmale

- Zwei 32-Bit-PCI-Busse mit 66 MHz

- 3,3-V-Core-Logikschaltung mit Universal-PCI-Schnittstellen, die mit 3,3-V- und 5-V-PCI-Signalisierungsumgebungen kompatibel sind

- Zweistufige interne Arbitrierung für bis zu neun sekundäre Bus-Master mit Unterstützung für einen externen sekundären Bus-Arbiter

- Zehn sekundäre PCI-Taktausgänge

- Unabhängige Lese- und Schreibbuffer für jede Richtung

- Burst-Datenübertragungen mit Pipeline-Architektur zur Maximierung des Datendurchsatzes in beide Richtungen

- Unterstützt die Schreibkombination für einen verbesserten Datendurchsatz

- Unterstützt die Frame-zu-Frame-Verzögerung von nur vier PCI-Taktgebern von einem zu einem anderen Bus

- Bis zu drei verzögerte Transaktionen in beide Richtungen

- Busverriegelungslaufzeit

- Vorhersehbare Latenz gemäß PCI-Local-Bus-Spezifikation

- Architektur konfigurierbar für PCI-Bus-Leistungsmanagement-Schnittstellenspezifikation

- CompactPCI-Hot-Swap-Funktionsumfang

- Der sekundäre Bus wird während dem Reset niedrig angesteuert

- VGA-/Palettenspeicher- und I/O-Dekodierungsoptionen

- Fortschrittliche stromsparende Submikron-CMOS-Technologie

- 208-Anschluss-PDV-, 208-Anschluss-PPM- oder 257-Anschluss-MicroStar-BGA™- Gehäuse

Blockdiagramm

Veröffentlichungsdatum: 2021-02-03

| Aktualisiert: 2022-03-11