Microchip Technology ZL3026x miClockSynth Universal-Taktgeneratoren

Microchip ZL3026x miClockSynth Universal-Taktgeneratoren verteilen mehrere Taktfrequenzen auf mehrere Lasten, was die Zuverlässigkeit des Designs verbessert, die BOM-Kosten reduziert und das Design vereinfacht. Die ZL3026x Bauteile erstellen einen komplexen Taktbaum und ersetzen mehrere Multiplikatoren, Synthesizer und Oszillatoren auf einem Board. Mit einem kleinen Gehäuse und einer erstklassigen jitter-Leistung sind diese Bauteile für Taktsynthese- und Frequenzumwandlungs-Applikationen mit harten jitter-Budgets und engen Boardplatzbeschränkungen ausgelegt.Merkmale

- 4 x flexible Eingangstakte

- 1 x Quarz-/CMOS-Eingang

- 2 x Differential-/CMOS-Eingänge

- 1 x einendiger/CMOS-Eingang

- Alle Eingangsfrequenzen von 9,72 MHz bis 1,25 GHz (300 MHz max. für CMOS)

- Aktivitätsmonitore, automatische/manuelle Schaltung

- Störungsfreie Taktschaltung über Pin oder Register

- Automatische Selbstkonfiguration beim Einschalten von externem oder internem EEPROM, bis zu 8 x Konfigurationen Pin-wählbar

- Externe Rückkopplung für Nullverzögerungsapplikationen

- Numerisch gesteuerter Oszillatormodus

- Frequenzspreizungsmodulationsmodus

- Erzeugt PCIe 1-, 2-, 3- und 4-konforme Taktgeber

- Einfach zu konfigurierendes Design erfordert keine externen VCXO- oder Schleifenfilter-Komponenten

- SPI- oder I2C-Prozessorschnittstelle

- Core-Versorgungsspannungsoptionen

- Nur 2,5 V

- Nur 3,3 V

- 1.8V+2.5V

- 1.8V+3.3V

- Platz sparender 8 mm2 QFN-56 mit 0,5 mm-Raster

- 6 x oder 10 x beliebige Frequenzen, beliebige Formatausgänge

- Jede Ausgangsfrequenz von 1 Hz bis 1.045 MHz

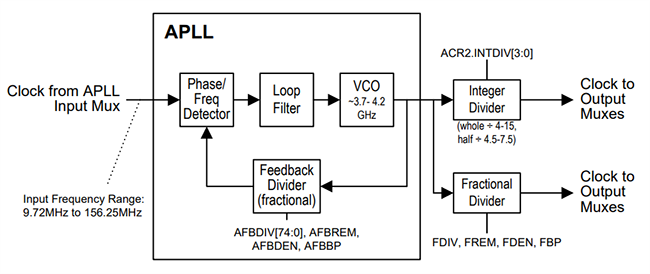

- Hochauflösende frac-N APLL mit 0-ppm-Fehler (ZL30260-ZL30263)

- Der APLL verfügt über einen fraktionalen Teiler und einen ganzzahligen Teiler, um zwei unabhängige Frequenzfamilien (ZL30260-ZL30263) zu erstellen

- 2 x Fractional-N-APLLs mit 0-ppm-Fehler (ZL30264-ZL30267)

- Jeder APLL verfügt über einen fraktionalen Teiler und einen ganzzahligen Teiler, um insgesamt vier unabhängige Frequenzfamilien (ZL30264-ZL30267) zu erstellen

- Ausgangs-Jitter

- Aus ganzzahliger Multiplikation und Teilern so niedrig wie 0,17 ps RMS (12 kHz bis 20 MHz)

- Aus fraktionierten Teilern ist typischerweise < 1 ps RMS, viele Frequenzen < 0, 5 ps RMS

- Jeder Ausgang verfügt über einen unabhängigen Teiler

- Jeder Ausgang ist als LVDS, LVPECL, HCSL, 2xCMOS oder HSTL konfigurierbar

- Im 2xCMOS-Modus können die P- und N-Pins verschiedene Frequenzen haben (z. B. 125 MHz und 25 MHz)

- Mehrere Ausgangsversorgungsspannungsbänke mit CMOS-Ausgangsspannungen von 1,5 V bis 3,3 V

- Präzise Schaltung zur Ausrichtung des Ausgangs und Einstellung der Phase je Ausgang

- Freigabe/Deaktivierung je Ausgang und störungsfreier Start/Stopp (Stopp hoch oder niedrig)

Applikationen

- Videoübertragung

- Industrielle Ethernet-Netzwerke

- Rechenzentren

- Infotainment

- Mensch-Maschine-Schnittstelle (HMI)

Technische Daten

- Versorgungsspannung

- 2,375 V bis 3,465 V Höherer Core-Bereich

- Niedriger Core-Bereich: 1,71 V bis 1,89 V

- I/O-Pin-Bereich ohne Taktgeber: 1,71 V bis 2,625 V

- OCx-Ausgangsbereich: 1,425 V bis 2,625 V

- Quarzoszillations-Frequenzbereich: 25 MHz bis 60 MHz

- Maximale Parallelkapazität von max. 5 pF, 2 pF (typisch)

- Lastkapazitätsbereich von 8 pF bis 16 pF , 10 pF (typisch)

- Äquivalenter Serienwiderstandsbereich (ESR): 50 Ω bis 60 Ω

- Maximale Quarzantriebsebenen (typisch): 100 µW, 200 µW und 300 µW

- Ungetaktete CMOS-Kontaktstifte

- ±10 µA Eingangs-/Ausgangs-Ableitstrom

- Maximale Eingangskapazität von 10 pF, 3 pF (typisch)

- Maximale Eingangshysterese von 11 pF, 3 pF (typisch)

- Taktausgang auf GPIO-Pin

- Frequenz: 50 MHz

- Typischer Anstiegs-/Abfallzeitbereich: 1,2 ns bis 2,3 ns

- XA-Takteingangs-Tastverhältnisbereich: 40 % bis 60 %

- Takteingänge

- Differenzieller Eingangsspannungsbereich: 0,1 V bis 1,4 V

- 1,35 VDC Typische Eingangsvorspannung, intern vorgespannt)

- Eingangsfrequenz

- 9,72 MHz bis 1250 MHz Differentialbereich

- Einendiger Bereich: 9,72 MHz bis 300 MHz

- Typischer Eingangswiderstand: 50 kΩ oder 80 kΩ

- LVDS-Taktausgänge

- Maximale Frequenz: 1.045 MHz

- Gleichtaktspannungsbereich: 1,13 V bis 1,37 V

- Differentialspannungsbereich: 310 mV bis 530 mV

- Typischer Anstiegs-/Abfallzeitbereich: 150 ps

- Tastverhältnisbereich: 45 % bis 55 %

- LVPECL-Taktausgänge

- Maximale Frequenz: 1.045 MHz

- Gleichtaktspannungsbereiche

- 1,13 V bis 1,33 V, wenn VDDOx = 2,5 V

- 1,85 V bis 2,05 V, wenn VDDOx = 3,5 V

- Differentialspannungsbereich: 650 mV bis 1.050 mV

- Typischer Anstiegs-/Abfallzeitbereich: 150 ps

- Tastverhältnisbereich: 45 % bis 55 %

- HCSL-Taktausgänge

- Maximale Frequenz: 250 MHz

- Gleichtaktspannungsbereich: 0,6 V bis 0,95 V

- Typischer Anstiegs-/Abfallzeitbereich: 250 ps

- Tastverhältnisbereich: 45 % bis 55 %

- CMOS- und HSTL-Taktausgänge (Klasse I)

- Maximaler Frequenzbereich: 1 Hz bis 250 MHz

- Typischer Anstiegs-/Abfallzeitbereich: 0,4 ns bis 2,2 ns

- Tastverhältnisbereich: 42 % bis 58 %

- Typischer Strom, wenn der Ausgang deaktiviert ist: 300 µA

- APLL-Frequenzen

- VCO-Bereich: 3.715 MHz bis 4.180 MHz

- PFD-Eingangsbereich: 9,72 MHz bis 156,25 MHz

- Jitter und Versatz

- Typische APLL-Jitter-Übertragungsbandbreite: 600 kHz

- Maximaler Versatz zwischen Ausgängen: 100 ps

- Betriebstemperaturbereich: -40 °C bis +85 °C

APLL Blockdiagramm

Weitere Ressourcen

Veröffentlichungsdatum: 2023-08-18

| Aktualisiert: 2023-08-22