Lattice Semiconductor Mach-NX FPGAs

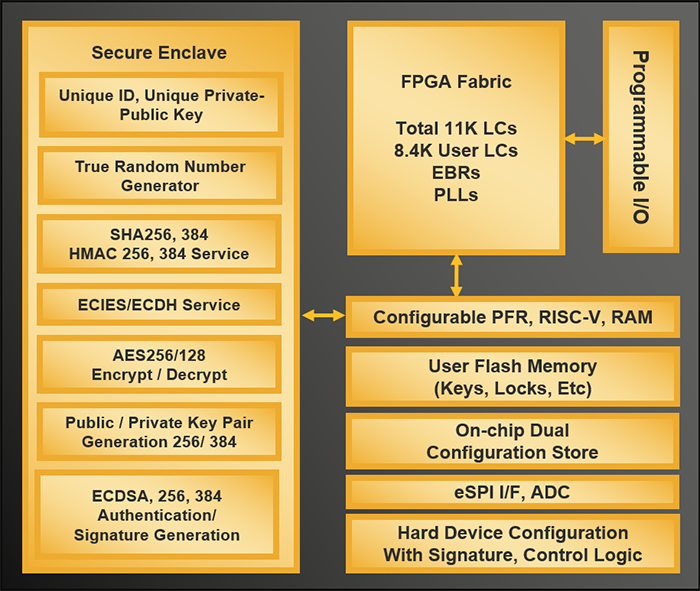

Lattice Semiconductor Mach-NX feldprogrammierbare Gate-Arrays sind FPGAs mit niedriger Dichte, einschließlich verbesserter Sicherheitsfunktionen und On-Chip-Dual-Boot-Flash, der aus SoC- und FPGA-Partitionen besteht. Die erweiterten Sicherheitsfunktionen umfassen AES-128/256 Advanced Encryption Standard (AES), Secure Hash Algorithmus (SHA) SHA-256/384, Elliptic Curve Digital Signature Algorithmus (ECDSA), Elliptic Curve Integrated Encryption Scheme (ECIES), Hash Message Authentication Code (HMAC) HMAC-SHA256/384, Public-Key-Kryptografie und eine einzigartige sichere ID.Die Mach-NX-FPGAs kombinieren eine sichere Enklave (eine fortschrittliche, 384-Bit Hardware-basierte Crypto-Engine, die einen umprogrammierbaren Bitstream-Sicherheit unterstützt) mit einer Logikzelle (LC) und einem I/O-block. Die sichere Enklave unterstützt die sichere Firmware und der LC und der I/O-Block ermöglichen Systemsteuerungsfunktionen, beispielsweise Leistungsmanagement und Lüftersteuerung. Die Bauelemente können Over-The-Air-Firmware-Updates verifizieren und installieren, damit Systeme mit den sich entwickelnden Sicherheitsrichtlinien und Protokollen konform sind. Die parallele Verarbeitungsarchitektur des Mach-NX FPGA und die Dual-Boot-Flash-Speicherkonfiguration bieten die nahezu sofortigen Reaktionszeiten, die zur Erkennung und Wiederherstellung von Angriffen erforderlich sind (ein Leistungsniveau, das über die Fähigkeiten anderer HRoT-Plattformen wie MCUs hinausgeht).

Die Mach-NX Bauteile von Lattice Semiconductor sind eine Root-of-Trust-Hardware-Lösung, die einfach erweitert werden kann, um das gesamte System mit verbesserter Bitstream-Sicherheit und Benutzermodusfunktionen zu schützen. Das Mach-NX Bauteil unterstützt die neuesten Industriestandard-I/O und bietet eine bahnbrechende I/O-Dichte mit einer hohen Anzahl von Optionen für die I/O-Programmierbarkeit.

Merkmale

- Bis zu 8,4 K LC von Benutzerlogik, 2669kbits Benutzer-flash-Speicher und eine dual-boot-flash-Funktion

- Bis zu 379 programmierbare I/O, die 1,2/1,5/1,8/2,5/3,3 I/O-Spannungen unterstützen

- Sichere Enklave unterstützt eine 384-bit-Kryptografie, einschließlich SHA, HMAC und ECC

- Die Konfiguration von PFR- und Sicherheitsfunktionen über Lattice Propel vereinfacht die Entwicklererfahrung

- Hohe Zuverlässigkeit, geringer Stromverbrauch und dreimal bessere SER-Leistung im Vergleich zu vergleichbaren CMOS-Technologien

Applikationen

- Sicheres Hochfahren und Root-of-Trust

- Rechen- und Speichersysteme

- Drahtlose Kommunikation

- Industrie-Steuerungssysteme

Technische Daten

- Lösungen

- Erstklassige Steuerungs-FPGA mit erweiterten Sicherheitsfunktionen bietet ein sicheres/authentifiziertes Hochfahren und eine Root-of-Trust-Funktion

- Optimierter Footprint, Logikdichte, I/O-Zähler, I/O-Leistungsbauteile für I/O-management und Logik-Applikationen

- Hohe I/O-Bauteile für I/O-Erweiterungsapplikationen

- Flexible Architektur mit hohem I/O-zu-LC-Verhältnis mit bis zu 379 I/O-pins

- Kryptografische sichere Enklave

- Advanced Encryption Standard (AES), AES-128/256 Verschlüsselung/Entschlüsselung

- Sicherer Hash-Algorithmus (SHA), SHA-256/384

- ECDSA-basierte Authentifizierung (Elliptic Curve Digital Signature Algorithmus, ECDSA)

- Hash-Nachrichten-Authentifizierungscode (HMAC), HMAC-SHA256

- Elliptic Curve Integrated Encryption Scheme (ECIs), ECIES-Verschlüsselung und -Entschlüsselung

- Echter Zufallsnummerngenerator (TRNG)

- Schlüsselmanagement mit Elliptic Curve Diffie-Hellman (ECDH) public-Key-Kryptografie

- Einzigartige sichere ID

- Schützt vor böswilligen Angriffen

- Mailbox-Schnittstelle zum SoC-Funktionsblock

- Federal Information Processing Standard (FIPS) unterstützt Sicherheitsprotokolle

- Flexibler I/O-Puffer mit hoher Leistungsfähigkeit

- Programmierbarer sysI/O™-buffer unterstützt eine große Auswahl von Schnittstellen auf ausgewählten Bänken

- LVCMOS 3,3/2,5/1,8/1,5/1,2

- LVTTL

- LVDS, Bus-LVDS, MLVDS und LVPECL

- Schmitt-trigger-Eingänge, bis zu 0,5 V Hysterese

- Ideal für I/O-Überbrückungsapplikationen

- Steuerung der langsamen/schnellen Anstiegsrate

- I/O-Unterstützung für hot-socketing

- Differentieller On-chip-Anschluss

- Programmierbarer pull-Up- oder pull-down-Modus

- Programmierbarer sysI/O™-buffer unterstützt eine große Auswahl von Schnittstellen auf ausgewählten Bänken

- Vorkonstruierter quellensynchroner I/O

- DDR-Register in I/O-Zellen

- Dedizierte Getriebelogik

- Generische DDR, DDRx2 und DDRx4

- 5 x Primärtakteingänge

- 8 x interne primäre Taktleitungen

- On-chip-Oszillator mit 5,5 % Genauigkeit

- 2x analoge PLLs pro Bauteil mit fractional-N-Frequenzsynthese, breitem Eingangsfrequenzbereich (7 MHz bis 400 MHz)

- IEEE Standard 1149,1 boundary-scan

- IEEE 1532-konforme in-system-Programmierung

- Nichtflüchtig, rekonfigurierbar

- Instant-on

- Multi-Sektorgesteuerter UFM für Kundendatenspeicherung

- Sichere Einzelchip-Lösung

- Programmierbar über JTAG, SPI oder I2C

- Rekonfigurierbarer Flash unterstützt die Hintergrundprogrammierung des nichtflüchtigen Speichers

- TransFR-Rekonfiguration, Vor-Ort-Logikaktualisierung, während I/O den Systemstatus auf ausgewählten Banken hält

- SoC-Funktionsblock

- 32-Bit-RISC-V-Prozessor mit on-chip-firmware-RAM und AHB-Lite-master-Schnittstelle

- Kryptografische sichere Enklave

- Gehärtete On-Chip-Funktionen

- SPI

- I2C

- Timer/Zähler

- PFR

Blockdiagramm