Infineon Technologies MoBL™ Extrem zuverlässige asynchrone SRAMs

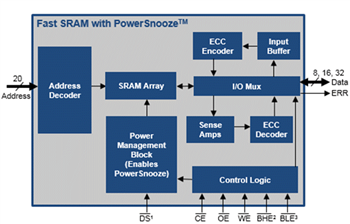

Die extrem zuverlässigen asynchronen MOBL™ -SRAMs von Infineon Technologies bieten eine Leistungsfähigkeit für eine große Auswahl von Industrie-, Kommunikations-, Datenverarbeitungs-, Medizintechnik-, Unterhaltungselektronik- und Militärapplikationen mit hoher Zuverlässigkeit. Diese SRAMs sind mit On-Chip-ECC erhältlich. Diese Bauteile sind hinsichtlich der Form und Funktion kompatibel mit asynchronen SRAMs der älteren Generation. Das ermöglicht es dem Benutzer, die Systemzuverlässigkeit zu verbessern, ohne in ein PCB-Neudesign zu investieren. Es handelt sich um die erste Gerätefamilie, welche die Zugriffszeit eines schnellen asynchronen SRAM mit einem einzigartigen extrem stromsparenden Schlafmodus (PowerSnooze™) kombiniert. Diese schnellen SRAMs von Infineon Technologies beseitigen den Kompromiss zwischen Leistung und Stromverbrauch in asynchronen SRAM-Anwendungen. Die besten Funktionen der bestehenden Produktfamilie werden durch die Bereitstellung eines neuartigen extrem stromsparenden Schlafmodus namens PowerSnooze ermöglicht. Der PowerSnooze ist ein zusätzlicher Betriebsmodus zu asynchronen Standard-SRAM-Betriebsmodi (Aktiv, Standby und Datenhaltung). Der Deep-Sleep-Pin (DS#) ermöglicht dem Bauelement den Wechsel zwischen dem Hochleistungs-Aktivmodus und dem extrem stromsparenden PowerSnooze-Modus. Mit einem niedrigen Tiefschlafstrom von 15 μA auf 4-MBit-Geräten kombiniert der schnelle SRAM mit PowerSnooze die besten Funktionen von schnellem und Micropower-SRAM in einem einzigen Bauelement.Diese asynchronen SRAM-Bauteile verwenden einen (38,32) Hamming-Code-ECC für die Einzelbit-Fehlererkennung und -korrektur. Der Hardware-ECC-Block in diesen extrem zuverlässigen asynchronen SRAMs führt alle ECC-bezogenen Funktionen Inline ohne Benutzereingriff aus. Extraterrestrische Strahlung mit höherer Energie kann mehrere benachbarte Bits umkippen, was zu Multi-Bit-Fehlern führen kann. Die Einzelbit-Fehlererkennung und Korrektur-Fähigkeit des Fehlerkorrekturcodes wird durch ein Bit-Verschachtelungsschema ergänzt, um das Auftreten von Mehrbitfehlern zu verhindern. Diese Funktionen verbessern gemeinsam die Leistung der Soft Error Rate (SER) erheblich, was zu branchenführenden FIT-Raten von weniger als 0,1 FIT/Mbit führt.

Merkmale

- Soft Error Rate < 0,1 FIT/Mbit für hohe Zuverlässigkeit

- ERR-Pin zur Anzeige von Einzelbit-Fehlern

- Dichteoptionen: 4 MBit, 8 MBit, 16 MBit

- 10 ns schnelle Zugriffszeit

- Extrem niedriger 8,7 μA-Standby-Strom (4 MBit MOBL)

- Busbreiten-Konfigurationen: x8, x16 und x32

- 1,8 V bis 5 V Bereich Betriebsspannungsbereich.

- Temperaturbereiche für Industrie und Automotive

Applikationen

- Industrieautomatisierung und -steuerung

- Multifunktions-Peripherie (MFP)

- Automotive-Infotainment

- Automotive-FAS