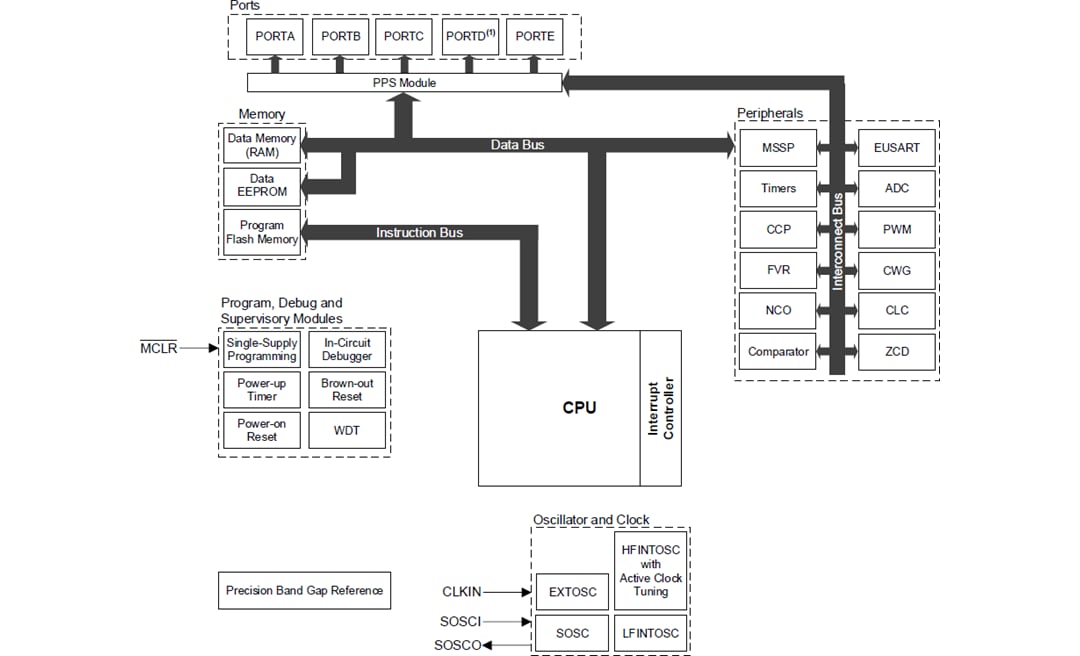

Microchip Technology PIC16F18056 und PIC16F18076 8-Bit-Mikrocontroller

Microchip Technology PIC16F18056 und PIC16F18076 8-Bit-Mikrocontroller verfügen über eine Suite von digitaler und analoger Peripherie, die kostengünstige Sensor- und Echtzeitsteuerungsapplikationen ermöglichen. Diese MCUs sind in 28-Pin- bis 44-Pin-Gehäusen mit einem Programm-Flash-Speicher von 28 kB und Geschwindigkeiten von bis zu 32 MHz verfügbar. Die PIC16F18056 und PIC16F18076 MCUs enthalten einen 10-Bit-Analog-Digital-Wandler mit Berechnung (ADCC), automatisierter kapazitiver Spannungsteilertechniken (CVD) für eine fortschrittliche kapazitive Berührungserkennung, Mittelung, Filterung, Überabtastung und einen Schwellenwertvergleich sowie eine Ladungspumpe zusätzlich zu einem 8-Bit-Digital-Analog-Wandler Modul (DAC).Die PIC16F18056 UND PIC16F18076 MCUs von Microchip Technology enthalten drei 10-Bit-Pulsweitenmodulationsmodule (PWM), eine Peripheriepinauswahl (PPS ), eine digitale Kommunikationsperipherie, Timer und Frequenzgeber. Darüber hinaus bieten diese Bauteile Speicherfunktionen, wie z. B. die Memory Access Partition (MAP) zur Unterstützung von Benutzern bei Datenschutz- und Bootloader-Applikationen. Daten-EEPROM und eine Device Information Area (DIA), die feste Spannungsreferenz-Offsetwerte (FVR) speichert, tragen zur Verbesserung der Genauigkeit des Analog-Digital-Wandlers (ADC) bei.

Der PIC16F18056 ist in 28-Pin-SPDIP-, SOIC-, SSOP- und VQFN-Gehäusen verfügbar. Der PIC16F18076 wird in 40-Pin-PDIP- und QFN-Gehäusen und in einem 44-Pin-TQFP-Gehäuse angeboten.

Merkmale

- Core-Merkmale

- C-Compiler-optimierte RISC-Architektur

- Betriebsgeschwindigkeit:

- DC bis 32MHz Takteingang

- 125 ns Befehlszeit (min.)

- 16-Level-Hardware-Stapel

- Stromsparendes Power-on-Reset (POR)

- Konfigurierbarer Power-Up-Timer (PWRT)

- Spannungsabfall-Reset (Brown-Out Reset, BOR)

- Watchdog-Timer (WDT)

- Speicher

- Bis zu 28 KB Programm-Flash-Speicher

- Bis zu 2 KB SRAM-Datenspeicher

- EEPROM-Datenspeicher mit bis zu 256 Byte

- Memory Access Partition (MAP) mit Programm-Flash-Speicher, unterteilt in:

- Applikationsblock

- Boot-Block

- Speicherbereich-Flash-Block (SAF)

- Programmierbarer Code- und Schreibschutz

- Die Device Information Area (DIA) speichert:

- Feste Spannungsreferenz-Messdaten (FVR)

- Microchip Einzigartiger Identifikator (MUI)

- Die Device Characteristics Area (DCI) speichert:

- Programm-/Lösch-Reihengrößen

- Pinzahl-Details

- Direkte, indirekte und relative Adressmodi

- Stromsparfunktionsumfang

- Schlafmodus

- Reduzierter Stromverbrauch des Bauteils

- Reduziertes elektrisches Systemrauschen während der Durchführung von ADC-Umwandlungen

- Stromsparende Modusfunktionen

- Schlafmodus

- < 900 nA (typisch) bei 3 V/25 °C (WDT-aktiviert)

- < 600 nA (typisch) bei 3 V/25 °C (WDT deaktiviert)

- Betriebsstrom

- 48 µA bei 32 kHz, 3 V/25 °C (typisch)

- < 1 mA bei 4 MHz, 5 V/25 °C (typisch)

- Schlafmodus

- Schlafmodus

- Taktstruktur

- Interner Oszillatorblock mit hoher Genauigkeit (HFINTOSC):

- Auswählbare Frequenzen von bis zu 32 MHz

- ±2 % bei Kalibrierung

- Interner 31-kHz-Oszillator (LFINTOSC)

- Externe Hochfrequenz-Takteingang

- Zwei externe Takt-Leisutngsmodi (EC)

- Sekundärer Oszillator (SOSC)

- Interner Oszillatorblock mit hoher Genauigkeit (HFINTOSC):

- Programmierungs- und Debug Funktionen

- In-Circuit-Serial-Programming™ (ICSP™) über zwei Pins

- In-Circuit-Debug (ICD) mit drei Breakpoints über zwei Pins

- Integriertes On-Chip-Debugging

- Betriebseigenschaften

- Betriebsspannungsbereich: 1,8 V bis 5,5 V

- Betriebstemperaturbereich

- Industrie: -40 °C bis +85 °C

- Erweitert: -40 °C bis +125 °C

- Gehäuseoptionen

- PIC16F18056: SPDIP-28, SOIC-28, SSOP-28, VQFN-28

- PIC16F18076: PDIP-40 -, QFN-40, TQFP-44

- Digitale Peripherie

- Zwei Capture/Compare/PWM(CCP)-Module

- 16-Bit-Auflösung für Capture-/Compare-Modi

- 10-Bit-Auflösung für Pulsweitenmodulatormodus (PWM)

- Drei Pulsbreitenmodulatoren (PWM)

- 10-Bit-Auflösung

- Vier konfigurierbare Logikzellen (CLC)

- Integrierte kombinatorische und sequentielle Logikschaltung

- Ein komplementärer Wellenform-Generator (CWG)

- Deadband-Steuerung mit steigender und fallender Flanke

- Vollbrücken-, Halbbrücken- und 1-Kanal-Antrieb

- Mehrere Signalquellen

- Programmierbares Totband

- Fehlerabschaltungseingang

- Ein konfigurierbarer 8-/16-Bit-Timer (TMR0)

- Zwei 16-Bit-Timer (TMR1/3) mit Gate-Steuerung

- Drei 8-Bit-Timer (TMR2/4/6) mit Hardwarebegrenzungs-Timer (HLT)

- Ein numerisch gesteuerter Oszillator (NCO)

- Erzeugt tatsächliche Frequenzregelung und erhöhte Frequenzauflösung

- Eingangstaktgeber von bis zu 64 MHz

- Bis zu zwei EUSARTs (Enhanced Universal Synchronous Asynchronous Receiver Transceiver, EUSART):

- RS-232-, RS-485- und LIN-kompatibel

- Automatische Aktivierung beim Start

- Bis zu zwei synchrone serielle Host-Anschlüsse (MSSP)

- Serieller Peripherieschnittstellenmodus (SPI)

- Inter-integrierter Schaltkreis-Modus (I2C)

- Periphere Pinauswahl (PPS)

- Geräte-I/O-Anschluss-Funktionen

- Bis zu 35 I/O-Pins

- Ein Nur-Eingangs-Pin

- Individuelle I/O-Richtung, Open-Drain, Eingangsschwellenwert, Anstiegsrate und schwache Pull-up-Steuerung

- Interrupt-on-Change (IOC) auf bis zu 25 Pins

- Ein externer Interrupt-Pin

- Zwei Capture/Compare/PWM(CCP)-Module

- Analoge Peripherie

- Analog-Digital-Wandler mit Berechnung (ADCC)

- 10-Bit-Auflösung

- Bis zu 35 externe Eingangskanäle

- Vier interne Eingangskanäle

- Interner ADC-Oszillator (ADCRC)

- Betrieb im Schlafmodus

- Auswählbare Auto-Konvertierungs-Trigger-Quellen

- Ladungspumpenmodul

- Verbessert die Genauigkeit von analogen Modulen bei Niederspannungen

- 8-Bit-Digital-Analog-Wandler (DAC)

- Ausgang auf einem I/O-Pin verfügbar

- Interne Verbindungen zu ADC und Komparatoren

- Ein Komparator (CMP)

- Bis zu vier externe Eingänge

- Konfigurierbare Ausgangspolarität

- Externer Ausgang über Peripherie-Pinauswahl

- Nulldurchgangserkennung (ZCD)

- Zwei feste Spannungsreferenzen (FVR)

- Analog-Digital-Wandler mit Berechnung (ADCC)

Applikationen

- Sensornetzwerke

- Echtzeit-Steuerapplikationen

- Benutzerschnittstelle

- Datenschutz

- Bootloader-Applikationen

- Industrieapplikationen

Videos

Blockdiagramm